AMBA APB 协议规范

AMBA APB 的协议翻译

发布信息

| 时间 | 版本号 | 保密性 | 变化 |

|---|---|---|---|

| 2023.09.05 | A | 无保密要求 | 第一次发布,v1.0 |

| 2004.08.17 | B | 无保密要求 | 第二次发布,v2.0 |

| 2010.04.13 | C | 无保密要求 | 第一次发布,v1.0 |

| 2021.05.09 | D | 无保密要求 | 为APB5版本加入了新功能 |

| 2023.02.28 | E | 无保密要求 | 在APB5版本加入了RME功能 |

Note:RME(Realm Management Extension)

引言

介绍了AMBA APB协议规范它包含以下部分:

关于规范

此规格是针对高级微控制器总线架构(AMBA)高级外设总线(APB)协议规格的。

目标受众

该规范是为希望熟悉AMBA APB协议的硬件和软件工程师编写的。

使用本规范

本规范组织如下章节:

第1章 介绍 :介绍了AMBA APB协议的概述第2章 信号介绍 :介绍APB的信号第3章 传输 :介绍APB的典型传输、错误响应和保护支持第4章 操作状态 :介绍APB的操作状态和变换第5章 接口奇偶校验保护 :介绍校验接口保护附录A 信号有效性 :介绍信号有效性的规则附录B 信号列表 :汇总了APB的信号附录C 版本 :介绍规范各个版本的变化。

约定

本节描述了本规格使用的约定:

排版

排版惯例是:

- italic(斜体):突出重要笔记,介绍特殊术语,并指示内部交叉引用和引用。

- bold(粗体):表示信号名称,并用于描述性列表中的术语(如果适用)。

- monospace(等宽):该字体用于汇编程序语法描述、伪代码和源代码示例。同时用于主要文本中的指令助记符,以及对出现在汇编程序语法描述、伪代码和源代码示例中的其他项目的引用。

- SMALL CAPITALS(小写大写字母):用于几个具有特定技术含义的术语。

时序图

时序图有时会同时将单比特信号显示为高电平和低电平,它们看起来与时序图约定中的总线变化相似。 如果时序图以这种方式显示单比特信号,则其值不会影响随附的描述。 阴影总线和信号区域是未定义的,因此总线或信号可以在该时间内的阴影区域内假设任何值。实际电平并不重要,也不影响正常操作。

信号

下面是关于信号方面的约定:

- 信号电平:断言信号的水平取决于信号是高有效还是低有效,断言意味着

- HIGH:表示高电平有效。

- LOW:表示低电平有效。

- 小写n:出现在信号名的开始或结束都表示低电平有效。

- 前缀H:表示AHB信号。

- 前缀P:表示APB信号。

数字

数字通常用十进制表示。二进制数字前加0b,而十六进制数字前加0x。

外链阅读

反馈

- 请通过填写 https://developer.arm.com/feedback/survey 上的表单,提交关于Arm产品文档的反馈意见。

- 有关Arm产品、架构和规格的技术反馈、问题或咨询,请在 https://support.developer.arm.com/my-cases/open-case/ 上提交支持请求。

第1章 介绍

本章提供了APB协议的概述。它包含以下几个部分:

1.1 关于APB

APB协议是一种低成本接口,优化了最小功耗和减少接口复杂性。 APB接口没有流水线,是一种简单的同步协议。 每次传输至少需要两个周期才能完成。

APB接口旨在访问外围设备的可编程控制寄存器。 APB外设通常通过APB桥连接到主存储系统。 例如,可以使用AXI到APB的桥将多个APB外设连接到AXI存储系统。

APB传输由APB桥启动。APB桥也可以称为请求者(主机)。 外设接口对请求作出响应。APB外设也可以称为完成者(从机)。本规范将使用请求者(主机)和完成者(从机)。

第2章 信号介绍

本章描述了AMBA APB信号。它包含以下部分:

2.1 AMBA APB 信号

本节描述了APB接口信号。

某些APB接口上的信号具有固定位宽,而某些信号可以具有多种位宽。 当位宽不是固定时,它通过属性进行描述。 如果属性值为零,这意味着该信号在接口上不存在。

表 2-1 提供了APB协议接口信号的描述。

表 2-1 APB 信号描述

| 信号名 | 信号源 | 位宽 | 描述 |

|---|---|---|---|

| PCLK | 时钟源 | 1 | 时钟。 PCLK是时钟信号。所有APB信号都在PCLK的上升沿进行采样。 |

| PRESETn | 复位源 | 1 | 复位。 PRESETn是复位信号,且为低有效信号。 PRESETn通常直接连接到系统总线复位信号。 |

| PADDR | 主机 | ADDR_WIDTH | 地址。PADDR是APB地址总线,PADDR位宽可以达到32位。 |

| PPROT | 主机 | 3 | 保护类型。 PPROT表示传输的正常、特权或安全保护级别,以及该传输是数据访问还是指令访问。详见 3.5 保护单元支持 |

| PNSE | 主机 | 1 | 扩展保护类型。详见 3.6 Realm扩展管理,RME |

| PSELx | 主机 | 1 | 选择。 主机为每个从机生成一个PSELx信号,PSELx表示从机被选择并且需要进行数据传输。 |

| PENABLE | 主机 | 1 | 使能。 PENABLE表示APB传输的第二个及后续周期。 |

| PWRITE | 主机 | 1 | 方向。 高电平PWRITE表示APB是写入访问,低电平PWRITE表示APB读取访问。 |

| PWDATA | 主机 | DATA_WIDTH | 写数据。 PWRITE写数据总线在写周期内由APB桥主机驱动,当PWRITE为高电平时PWDATA可以是8位、16位或32位宽。 |

| PSTRB | 主机 | DATA_WIDTH/8 | 脉冲写信号。 PSTRB 指示在写传输期间要更新哪些字节通道。每 8 位写数据总线有一个写使能信号。PSTRB[n]对应于PWDATA[(8n + 7):(8n)]。在读传输期间,PSTRB不能处于活动状态。详见 3.2 脉冲写 |

| PREADY | 从机 | 1 | 准备。 PREADY用于从机扩展APB传输。 |

| PRDATA | 从机 | DATA_WIDTH | 读取数据。 在PWRITE为低时,PRDATA读取数据总线由所选的从机在读取周期内驱动,PRDATA可以是8位、16位或32位宽。 |

| PSLVERR | 从机 | 1 | 传输错误。PSLVERR是一个可选信号,可以由主机断言为高电平,以指示APB传输出现错误。详见 3.4 ERROR响应 |

| PWAKEUP | 主机 | 1 | 唤醒。 PWAKEUP指的是与APB接口相关的任何唤醒动作。详见 3.7 唤醒信号 |

| PAUSER | 主机 | USER_REQ_WIDTH | user请求属性。 建议PAUSER的最大位宽为128位。 详见 3.8 user信号 |

| PWUSER | 主机 | USER_DATA_WIDTH | user写数据属性。 建议PWUSER的最大位宽为DATA_WIDTH/2。详见 3.8 user信号 |

| PRUSER | 从机 | USER_DATA_WIDTH | user读数据属性。 建议PRUSER的最大位宽为DATA_WIDTH/2。详见 3.8 user信号 |

| PBUSER | 从机 | USER_RESP_WIDTH | user响应属性。PBUSER建议最大位宽为16位。详见 3.8 user信号 |

2.1.1 地址总线

APB接口有一个单一的地址总线PADDR用于读写传输。PADDR表示字节地址。

PADDR可以与数据位宽不对齐,但结果是不可预测的。 例如,一个从机可能使用未对齐的地址、对齐的地址,发出错误响应。

[ For example, a Subordinate might use the unaligned address, aligned address, or signal an error response.]

2.1.2 数据总线

APB协议具有两个独立的数据总线,PRDATA用于读取数据,PWDATA用于写入数据。 这些总线可以是8位、16位或32位宽。 读取数据总线和写入数据总线必须具有相同的位宽。

数据传输不能同时进行,因为读取数据和写入数据总线没有各自独立的握手信号。

第3章 传输

本章描述了典型的AMBA APB传输、错误响应和保护单元支持,包含以下各节:

3.1 写传输

本节描述以下几种写入传输类型:

本节中显示的所有信号都在PCLK的上升沿采样。

3.1.1 无等待写

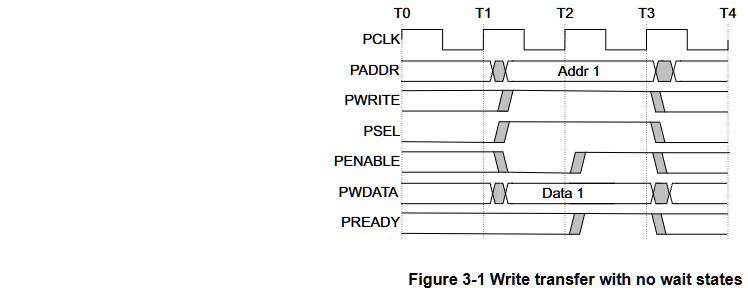

图 3-1 显示了一个没有等待状态的基本写入传输。

在 图 3-1 中:

- T0-T1:无动作。

- T1-T2:主机请求对地址Addr1发起strong>PWRITE为高的Setup阶段写传输。从机无动作。

- T2-T3:主机请求对地址Addr1发起PENABLE为高的Access阶段写传输。从机拉高PREADY完成地址Addr1的传输。

- T3-T4:无动作。

写入传输的Setup阶段发生在 图 3-1 中的T1处。 选择信号PSELx被断言(拉高), 这意味着PADDR、strong>PWRITE和PWDATA必须是有效的。

写入传输的Access阶段在 图 2-1 中的T2处显示,在此期间PENABLE被断言(拉高)。 PREADY在PCLK上升沿由从机断言(拉高),以表示写入数据将在T3处被接受。 PADDR、PWDATA和其他任何控制信号必须稳定,直到传输完成。

在传输结束时,PENABLE被解除断言(拉低)。除非存在另一个传输到同一外设,否则PSELx也被解除断言(拉低)。

3.1.2 有等待写

图 3-2 显示了从机如何使用PREADY来扩展写传输。

在 图 3-2 中

- T0-T1:无动作。

- T1-T2:主机请求对地址Addr1发起strong>PWRITE为高的Setup阶段写传输。从机无动作。

- T2-T3:主机请求对地址Addr1发起PENABLE为高的Access阶段写传输。从机拉低PREADY请求主机对传输插入一个等待周期。

- T3-T4:主机保持不变。从机保持不变。

- T4-T5:主机保持不变。从机拉高PREADY完成地址Addr1的传输。

- T5-T6:无动作。

在Access阶段,当PENABLE为高时,从机通过将PREADY拉低来扩展传输。

在PREADY为低时,以下信号保持不变:

- 地址信号,PADDR

- 方向信号,PWRITE

- 选择信号,PSELx

- 使能信号,PENABLE

- 写数据信号,PWDATA

- 写脉冲信号,PSTRB

- 保护类型信号,PPROT

- 用户请求属性,PAUSER

- 用户写数据属性,PWUSER

当PENABLE为低时,PREADY可以取任何值。 这确保了具有固定两个周期访问的外设可以将PREADY拉高。

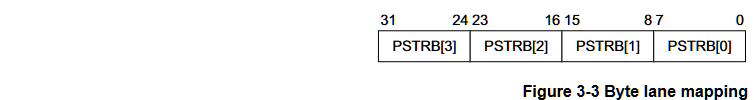

3.2 脉冲写

PSTRB使得写数据总线上的稀疏数据传输成为可能。 每个PSTRB对应于写数据总线的1个字节。 当PSTRB某个bit断言为高电平时,表示写数据总线相应的字节通道包含有效信息。

每8位写数据总线都与一个PSTRB bit对应, 因此PSTRB[n]对应于PWDATA[(8n + 7):(8n)]。

图 3-3 展示了在 32 位数据总线上的这种关系。

对于读取传输,请求者必须将所有PSTRB位拉低。

3.2.1 PSTRB的兼容性

PSTRB是一个可选信号。 APB外设可能支持有限的访问类型,这些类型必须记录给程序员。 这意味着如果该文档声明不支持稀疏写入,则所有PSTRB存在的组合可能是兼容的。 当连接主机和从机时,PSTRB的兼容性描述在 表 3-1 。

表 3-1 PSTRB的存在与兼容性

| PSTRB | 从机不存在该信号 | 从机存在该信号 |

|---|---|---|

| 主机不存在该信号 | 兼容。不支持稀疏写。 | 兼容.所有写数据字节通道在写入时均有效。PSTRB应该与PWDATA直接连接。 |

| 主机存在该信号 | 兼容。不支持稀疏写。 | 兼容。不支持稀疏写. |

3.3 读传输

包含有两种读方式:

本节中显示的所有信号都在PCLK的上升沿采样。

3.3.1 无等待读传输

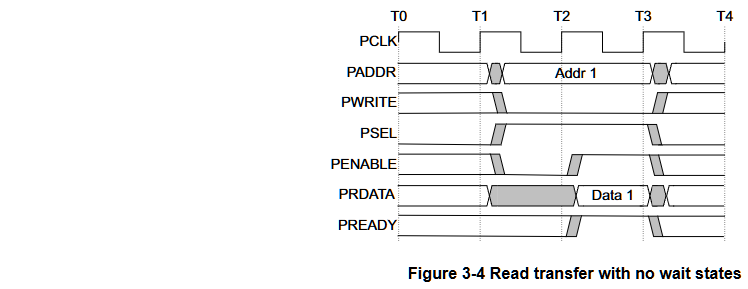

图 3-4 显示了无等待读取传输。

在 图 3-4 中:

- T0-T1:无动作。

- T1-T2:主机请求对地址Addr1发起strong>PWRITE为低的Setup阶段读传输。从机无动作。

- T2-T3:主机请求对地址Addr1发起PENABLE为高的Access阶段读传输。从机拉高PREADY完成地址Addr1的传输。

- T3-T4:无动作。

地址信号PADDR、写信号PWRITE、选择信号PSELx和 使能信号PENABLE的时序与 3.1.1 无等待写传输 描述的相似。 主机必须在读传输结束之前提供数据。

3.3.2 有等待读

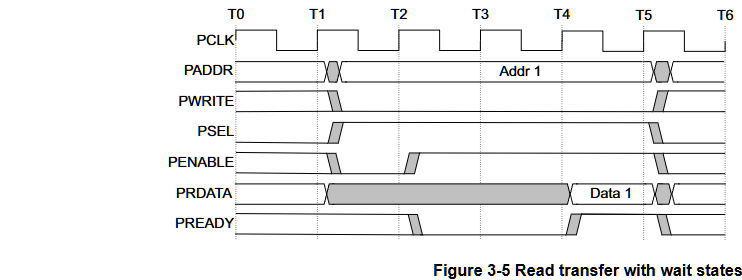

图 3-5 展示了PREADY信号如何扩展读传输。

在 图 3-5 中

- T0-T1:无动作。

- T1-T2:主机请求对地址Addr1发起strong>PWRITE为低的Setup阶段读传输。从机无动作。

- T2-T3:主机请求对地址Addr1发起PENABLE为高的Access阶段读传输。从机拉低PREADY请求主机对传输插入一个等待周期。

- T3-T4:主机保持不变。从机保持不变。

- T4-T5:保持不变。从机拉高PREADY完成地址Addr1的传输。

- T5-T6:无动作。

如果在Access阶段期间将PREADY拉低,则传输将延长。 以下信号在PREADY保持拉低时保持不变:

- 地址信号,PADDR

- 方向信号,PWRITE

- 选择信号,PSELx

- 使能信号,PENABLE

- 保护信号,PPROT

- 用户信号,PAUSER

图 3-5 显示使用PREADY添加了两个周期等待。 然而,可以添加任意数量的额外周期实现等待操作。

3.4 ERROR响应

PSLVERR可用于表示APB传输中的错误状态。错误状态可以在读和写传输中发生。

PSLVERR仅在APB传输的最后一个周期内被视为有效, 此时PSELx、PENABLE和PREADY均为高电平。

建议,但不要求,当PSELx、PENABLE或PREADY为低电平时, 将PSLVERR驱动为低电平。

收到错误的传输可能已经或未改变外设的状态, 相对于于外设来说,两种状态都是可以接受的。 当写传输收到错误时,并不意味着外设内的寄存器没有被更新。

收到错误的读传输可能返回无效数据, 对于读错误,外设没有必要将数据总线驱动为全0。

收到读传输错误响应的主机仍然可以使用该数据。 从机不能依赖错误响应来阻止读取PRDATA上的值。

从机不强制支持PSLVERR。 如果主机不包含PSLVERR, 则主机的相应输入应该被连接为低电平。

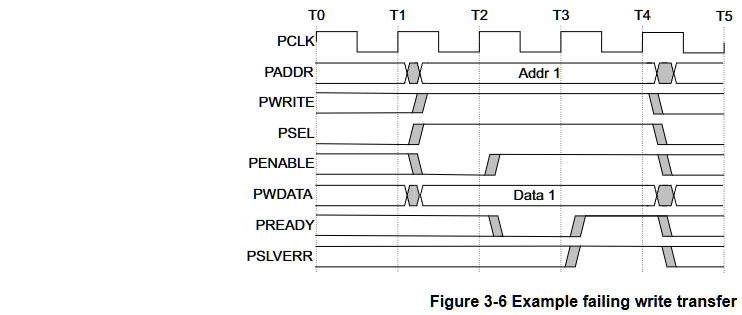

3.4.1 写传输

图 3-6 显示了一个失败的写入传输示例,该传输以错误结束。

在 图 3-6 中

- T0-T1:无动作。

- T1-T2:主机请求对地址Addr1发起strong>PWRITE为高的Setup阶段写传输。从机无动作。

- T2-T3:主机请求对地址Addr1发起PENABLE为高的Access阶段写传输。从机拉低PREADY请求主机对传输插入一个等待周期。

- T4-T5:主机保持不变。从机拉高PREADY和PSLVERR完成地址Addr1的失败传输。

- T5-T6:无动作。

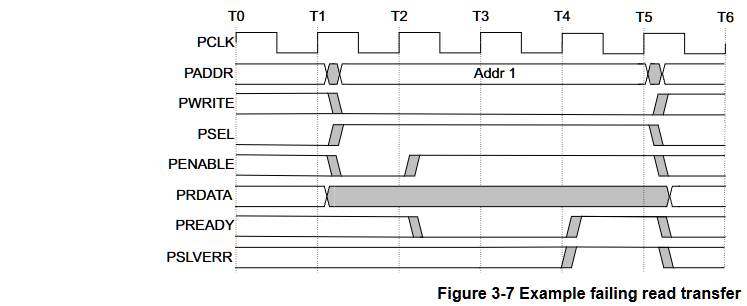

3.4.2 读传输

读取传输也可以用ERROR响应完成,表示没有有效的读取数据可用。 图 3-7 显示了一个以ERROR响应完成的读取传输。

在 图 3-7 中

- T0-T1:无动作。

- T1-T2:主机请求对地址Addr1发起strong>PWRITE为低的Setup阶段读传输。从机无动作。

- T2-T3:主机请求对地址Addr1发起PENABLE为高的Access阶段读传输。从机拉低PREADY请求主机对传输插入一个等待周期。

- T3-T4:主机保持不变。从机保持不变。

- T4-T5:保持不变。从机拉高PREADY和PSLVERR完成地址Addr1的ERROR传输。

- T5-T6:无动作。

3.4.3 PSLVERR的映射

当进行桥接时:

- 从AXI到APB: 在PSLVERR上的APB错误被映射回AXI读取的RRESP和写入的BRESP。

- 从AHB到APB: 在PSLVERR上的APB错误被映射回AHB读取和写入的HRESP。

3.5 保护单元支持

为了支持复杂的系统设计,通常需要系统中的互连和其他设备提供对非法交易的保护。 对于APB接口,这种保护通过PPROT[2:0]信号提供。 表 3-2 显示了三种访问保护级别及其保护级别编码。

表 3-2 访问保护

| PPROT | 保护类型 | 描述 | 信号值和对应保护类型 |

|---|---|---|---|

| PPROT[0] | Normal或Privileged | PPROT[0]被主机用来表示处理模式。特权处理模式通常在系统中具有更高的访问级别。 | LOW:normal HIGH:privileged |

| PPROT[1] | Secure或Non-secure | PPROT[1]用于需要在处理模式之间具有更大区分度的系统。 | LOW:secure HIGH:None-secure |

| PPROT[2] | Data或Instruction | PPROT[0]用于表示该传输是否为数据或指令访问,传输表示作为提示提供,在所有情况下并不一定准确 | LOW:data HIGH:Inst |

Note:PPROT的主要用途是作为安全或非安全交易的标识符。 使用不同的PPROT[0]和PPROT[2]标识符的解释是可以接受的。

3.5.1 PPROT的存在和兼容性

PPROT是主机和从机接口上的一个可选信号。 表 3-3 描述了连接主机到从机时的PPROT兼容性表现。

表 3-3 PPROT[0]的存在和兼容性

| PPROT | 从机不存在该信号 | 从机存在该信号 |

|---|---|---|

| 主机不存在该信号 | 兼容 | 不兼容,如果在功能上保证了正确就是兼容的。详见 表 3-2 |

| 主机存在该信号 | 兼容,从机无法访问该信号,因此该信号可以被忽略。 | 兼容 |

3.6 Realm管理扩展,RME

本节描述了APB协议对Arm ® Realm Management Extension (RME)系统架构的支持。 RME是ARM TrustZoon架构的一部分。

3.6.1 Root和Realm 物理地址空间

RME将Root和Realm物理地址空间添加到Arm架构中。 这些可以在APB事务的权限检查中使用。 表 3-4 列出了为支持RME而在APB5接口上添加的额外信号。

表 3-4 PNSE信号描述

| 信号 | 位宽 | 信号源 | 描述 |

|---|---|---|---|

| PNSE | 1 | 主机 | 扩展保护类型。当PSELx被断言(拉高)时PNSE必须有效 |

表 3-5 列出了PNSE和PPROT的允许组合, 这些组合决定了事务的物理地址空间。

表 3-5 PNSE和PPROT[1]决定了传输的物理地址空间

| PNSE | PPROT[1] | 物理地址空间 |

|---|---|---|

| 0 | 0 | Secure |

| 0 | 1 | Non-secure |

| 1 | 0 | Root |

| 1 | 1 | Realm |

3.6.2 配置

RME_Support 属性用于表示 APB 接口是否支持 RME:

- True:RME是支持的,PNSE信号在接口上存在,且能在APB5接口上使用。

- False:RME不支持。PNSE信号在接口上不存在,如果在接口上未声明RME_Support属性,则视为False。

如果PNSE存在于接口上,PPROT也必须存在。

PNSE信号使用PCTRLCHK信号进行奇偶校验保护。

表 3-6 列出了依据RME_Support属性的值,主机和从机接口之间的兼容性,

表 3-6 RME_Support 存在和兼容性

| RME_Support | 从机不存在该信号 | 从机存在该信号 |

|---|---|---|

| 主机不存在该信号 | 兼容 | 兼容。PNSE绑定为LOW |

| 主机存在该信号 | 不兼容 | 兼容 |

3.7 唤醒信号

本节描述了在APB接口中使用的唤醒信号。

3.7.1 介绍

唤醒信号PWAKEUP用于表示与任何APB接口关联的任何唤醒行为。

PWAKEUP提供一个无毛刺的信号,可以路由到时钟控制器或类似组件, 以使连接组件的电源和时钟启用Wakeup_Signal属性用于表示组件是否支持唤醒信号:

- True:存在唤醒信号

- False 不存在唤醒信号。如果未声明Wakeup_Signal属性,则视为False。

唤醒信号只能添加到APB5协议接口。

3.7.2 唤醒信号

表 3-7 描述了PWAKEUP信号。

表 3-7 PWAKEUP信号描述

| 信号 | 位宽 | 信号源 | 描述 |

|---|---|---|---|

| PWAKEUP | 1 | 主机 | PWAKEUP指与主机接口相关的任何唤醒行为。 |

PWAKEUP的规则和建议如下:

- PWAKEUP与PCLK同步,必须在与其不同的时钟域中异步采样, 这是PWAKEUP无毛刺所需要的。例如,可以通过直接从寄存器生成或通过无毛刺的OR树来实现。

- PWAKEUP可以在PSELx断言之前、期间或之后被断言。

- 在PREADY断言之前,允许主机等待PWAKEUP被断言。 如果PWAKEUP存在但从未被断言,接口可能会出现死锁。

- 如果PWAKEUP和PSELx在同一个周期内均为HIGH, PWAKEUP必须保持被断言状态,直至PREADY被断言。

- 建议在断言PSELx之前至少提前一个周期断言PWAKEUP,以防止新传输被延迟。

- 建议在不再需要进一步传输时解除PWAKEUP的断言。

- 允许但不建议在没有发生传输的情况下先断言PWAKEUP再解除其断言。

- 建议连接的主机和从机的时钟一起进行时钟门控。 如果从机接口的时钟与主机时钟独立门控,并且使用PWAKEUP启用从机时钟, 则存在从机错过传输的Setup阶段的可能性。

3.8 user信号

本节描述了APB接口中的user信号。

3.8.1 介绍

APB协议的用户可能会遇到一个需要添加未在APB协议中指定的信令的应用程序。 user信号定义了一种将此信号添加到传输的标准方法,而不定义信号的使用。

通常建议不要使用user信号。APB协议接口并未定义这些信号的功能, 如果两个组件以不兼容的方式使用相同的user信号,将导致互操作性问题。

user信号只能添加到APB5协议接口。

3.8.2 信号

所有信号都是可选的。如果相关的位宽属性为零,则信号不存在。

| 信号 | 位宽 | 信号源 | 描述 |

|---|---|---|---|

| PAUSER | USER_REQ_WIDTH | 主机 | 用户定义的请求。 当PSELx被断言(拉高)时,PAUSER必须有效。 在一次传输的Setup和Access阶段内PAUSER值必须保持不变。 在Access阶段内部的每一个周期PAUSER也必须保持不变。 |

| PWUSER | USER_DATA_WIDTH | 主机 | 用户定义的写数据。 当PSELx和PWRITE被断言时,PWUSER必须有效。 在一次传输的Setup和Access阶段内PWUSER值必须保持不变。 在Access阶段内部的每一个周期PWUSER也必须保持不变。 |

| PRUSER | USER_DATA_WIDTH | 从机 | 用户定义的读数据。 当PSELx、PENABLE、PREADY被断言时,PWRITE被解除断言(拉低)时,PRUSER必须有效。 |

| PBUSER | USER_RESP_WIDTH | 从机 | 用户定义的响应。 当PSELx、PENABLE、PREADY被断言时,PBUSER必须有效。 |

3.8.3 user信号的建议

在user信号被实现的地方,本规范不要求支持所有user信号。 user信号的位宽由实现决定,并且请求、数据和响应的位宽可以不同。

建议在域跨越的桥或互连上包含所有user信号的支持。 然而,从机上没有要求必须包括它们。

建议USER_DATA_WIDTH是数据总线位宽的整数倍(以字节为单位),便于进行数据位宽和协议转换。

第4章 操作状态

本章描述了AMBA APB的操作状态。它包含以下部分:

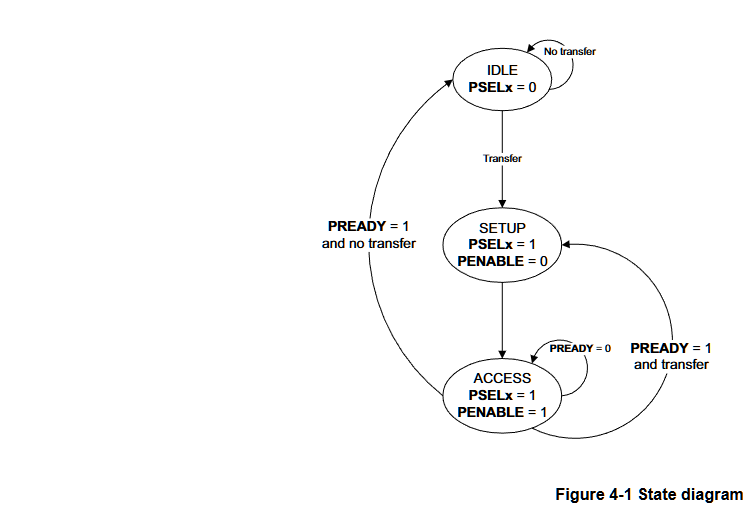

4.1 操作状态

图 4-1 展示了APB接口的操作状态。

状态机通过以下状态进行操作:

- IDLE:这是APB接口的默认状态。

- SETUP:当需要传输时,接口会进入SETUP状态,此时选择信号PSELx被断言。 接口只在SETUP状态停留一个时钟周期,并且总是在下一个时钟上升沿移动到ACCESS状态。

- ACCESS:在ACCESS状态中,使能信号PENABLE被断言。

在SETUP和ACCESS之间的转变以及ACCESS状态中的周期之间,以下信号必须保持不变:

- PADDR

- PPROT

- PWRITE

- PWDATA,仅针对写传输。

- PSTRB

- PAUSER

- PWUSERACCESS状态的退出由来自从机的PREADY信号所控制。如果从机将PREADY拉低,则保持ACCESS状态。如果从机将PREADY拉高,则退出ACCESS状态,如果不再需要传输,总线返回到IDLE状态。 如果另一个传输跟随,则总线直接移动到SETUP状态。

第5章 奇偶校验接口保护

本章描述了一种用于检测组件之间接口上单比特错误的奇偶校验方案。它包含以下几个部分:

5.1 接口保护

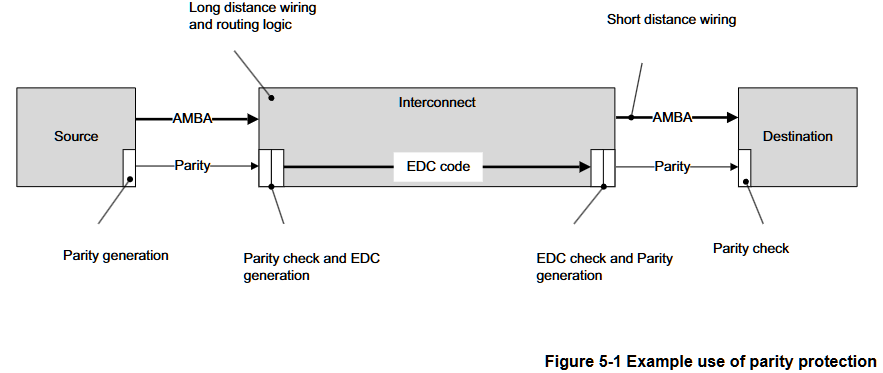

对于安全关键应用,必须在SoC内部的单个线路上检测和纠正瞬态和功能错误。

系统组件中的错误可能会传播并导致连接组件之间出现多个错误。 需要端到端的错误检测与纠正(EDC),覆盖从源到目的地的所有逻辑和线路。

实现端到端保护的一种方法是在组件中使用定制的EDC方案,并在组件之间实施简单的错误检测方案。 在这些组件之间没有逻辑,单比特错误不会传播为多比特错误。 本节描述了一种在组件之间接口上检测单比特错误的奇偶校验方案。 如果多比特错误发生在不同的奇偶校验信号组中,则可以检测到这些错误。

图 5-1 显示了可以使用奇偶校验的位置。

5.2 接口保护配置

接口的EDC方案由Check_Type属性定义。以下是定义的Check_Type值:

- False:接口上没有检测信号。

- Odd_Parity_Byte_All:所有信号都包含奇数奇偶校验。 奇偶校验信号的每一位覆盖最多8位。

如果未声明Check_Type,则视为False。

检测信号仅可以添加到APB5接口中。

5.3 奇偶校验检查

以下属性是为字节奇偶校验接口保护所添加检查信号的共同特征:

- 使用奇数奇偶校验时。奇数奇偶校验意味着在接口信号和检查信号中,总是存在奇数个比特被断言(高)。检查信号与每个接口信号相关联。

- 每个校验bit覆盖的有效payload bit不超过8位。这个限制假设在生成每个校验比特的时间余量中最多有三个逻辑电平可用。

- 涉及关键控制信号的奇偶校验信号由一个单独的奇偶校验bit定义。单个奇偶校验bit是原始关键控制信号的反转。关键控制信号可能只有较小的时间余量可用。

- 对于宽度超过1位的检查信号:

- 检查比特[n]对应于有效payload中的[(8n+7):8n]。

- 如果有效payload不是整数个字节,则检查信号的最高有效位覆盖有效payload中少于8位的最高有效部分。

- 检查信号必须在每个检查使能项为真时正确驱动。请参见 表 5-1 。

- 有效payload的所有bit对应的校验信号必须适当地驱动,无论这些bit在传输中是否被使用。例如,PWDATACHK的所有bit必须正确驱动,即使某些字节不是有效数据字节。

- 如果被检查信号覆盖的一些信号在接口上不存在,则假定缺失的信号为低电平。

- 如果被检查信号覆盖的信号在接口上都不存在,则检查信号被省略。

5.4 错误检测

该规范并不规定在检测到校验错误时组件或系统的行为。 根据系统和受影响的信号,翻转的bit可以产生不同的影响。 它可能是无害的,导致性能问题,导致数据损坏,导致安全违规或死锁。

当检测到错误时,从机可以:

- 终止或传播传输。

- 修正奇偶校验信号或传播错误。

- 更新其内存或保持不变。

- 通过其他方式发出错误响应,例如通过中断。

5.5 校验检查信号

检查信号与PCLK同步,并且必须在检查使能项为真时的每个周期都被正确驱动。

表 5-1 显示了奇偶校验检查信号。

表 5-1 奇偶校验检查信号

| check信号 | 相关联的信号 | 位宽 | 颗粒度 | check使能 |

|---|---|---|---|---|

| PADDRCHK | PADDR | ceil(ADDR_WIDTH/8) | 1-8 | PSEL |

| PCTRLCHK | PPROT、PWRITE、PNSE | 1 | 1-5 | PSEL |

| PSELxCHK | PSELx | 1 | 1 | PRESETn |

| PENABLECHK | PENABLE | 1 | 1 | PSEL |

| PWDATACHK | PWDATA | DATA_WIDTH/8 | 8 | PSELx&PWRITE |

| PSTRBCHK | PSTRB | 1 | 1-4 | PSELx&PWRITE |

| PREADYCHK | PREADY | 1 | 1 | PSELx&PENABLE |

| PRDATACHK | PRDATA | DATA_WIDTH/8 | 8 | PSEL&PENABLE&PREADY&!PWRITE |

| PSLVERRCHK | PSLVERR | 1 | 1 | PSEL&PENABLE&PREADY |

| PWAKEUPCHK | PWAKEUP | 1 | 1 | PRESETn |

| PAUSERCHK | PAUSER | ceil(USER_REQ_WIDTH/8) | 1-8 | PSELx |

| PWUSERCHK | PAUSER | ceil(USER_DATA_WIDTH/8 | 1-8 | PSELx&PWRITE |

| PRUSERCHK | PRUSER | ceil(USER_DATA_WIDTH/8) | 1-8 | PSELx&PENABLE&PREADY&!PWRITE |

| PBUSERCHK | PBUSER | ceil(USER_RESP_WIDTH/8) | 1-8 | PSELx&PENABLE&PREADY |

Note:ceil()表示对括号内的数值向下取整。 Note:需对PSEL分开检查,是由于只有一个PSEL会路由到每个从机。

附录A 信号有效性

本附录总结了描述信号何时必须有效的规则

A.1 有效性规则

下面信号必须总是有效:

- PSELx

- PWAKEUP

当PSELx断言(高)时,下面信号必须有效:

- PADDR

- PPROT

- PNSE

- PENABLE

- PWRITE

- PAUSER

- PSTRB

- PWDATA(只在写传输)

- PWUSER(只在写传输)

当PSELx和PENABLE断言时,下面信号必须有效:

- PREADY

当PSELx、PENABLE、PREADY断言时,下面信号必须有效:

- PRDATA(只在读传输)

- PSLVERR

- PRUSER(只在读传输)

- PBUSER

建议将不需要为有效的信号驱动为零。

附录B 信号列表

本附录提供了APB接口上所有信号的摘要。

B.1 APB信号

表 B-1 描述了APB信号的列表。 表 B-2 描述了APB检查信号的列表。可选信号有一个默认值,应用于任何未驱动输入。

- Y: 强制。

- N: 不得存在。

- O: 输入和输出可选。

- OO:对输出端口可选,对输入端口强制。

- C: 条件性的。如果属性为真,则必须存在。

- OC:条件性,可选性。可选性只能在属性为真时存在。

表 B-1 APB信号

| signal | width | default | property | APB5 | apb4 | APB3 | APB2 |

|---|---|---|---|---|---|---|---|

| PCLK | 1 | - | - | Y | Y | Y | Y |

| PRESETn | 1 | - | - | Y | Y | Y | Y |

| PADDR | ADDR_WIDTH | - | - | Y | Y | Y | Y |

| PPROT | 3 | 0b000 | − | O | O | N | N |

| PNSE | 1 | 0b0 | RME_Support | C | N | N | N |

| PSELx | 1 | − | − | Y | Y | Y | Y |

| PENABLE | 1 | − | − | Y | Y | Y | Y |

| PWRITE | 1 | − | − | Y | Y | Y | Y |

| PWDATA | DATA_WIDTH | − | − | Y | Y | Y | Y |

| PSTRB | DATA_WIDTH/8 | − | − | O | O | N | N |

| PREADY | 1 | 0b1 | − | OO | OO | OO | N |

| PRDATA | DATA_WIDTH | 0b0 | − | Y | Y | Y | Y |

| PSLVERR | 1 | 0b0 | − | OO | OO | OO | N |

| PWAKEUP | 1 | − | Wakeup_signal | C | N | N | N |

| PAUSER | USER_REQ_WIDTH | − | USER_REQ_WIDTH | OC | N | N | N |

| PWUSER | USER_DATA_WIDTH | − | USER_DATA_WIDTH | OC | N | N | N |

| PRUSER | USER_DATA_WIDTH | − | USER_DATA_WIDTH | OC | N | N | N |

| PBUSER | USER_RESP_WIDTH | − | USER_RESP_WIDTH | OC | N | N | N |

表 B-2 检查信号

| signal | width | property | APB5 | apb4 | APB3 | APB2 |

|---|---|---|---|---|---|---|

| PADDRCHK | ADDR_WIDTH/8 | Check_Type | C | N | N | N |

| PCTRLCHK | 1 | Check_Type | C | N | N | N |

| PSELxCHK | 1 | Check_Type | C | N | N | N |

| PENABLECHK | 1 | Check_Type | C | N | N | N |

| PWDATACHK | DATA_WIDTH/8 | Check_Type | C | N | N | N |

| PSTRBCHK | 1 | Check_Type | C | N | N | N |

| PREADYCHK | 1 | Check_Type | C | N | N | N |

| PRDATACHK | DATA_WIDTH/8 | Check_Type | C | N | N | N |

| PSLVERRCHK | 1 | Check_Type | OC | N | N | N |

| PWAKEUPCHK | 1 | Check_Type & Wakeup_Signal | C | N | N | N |

| PAUSERCHK | ceil(USER_REQ_WIDTH/8) | Check_Type & USER_REQ_WIDTH | OC | N | N | N |

| PWUSERCHK | ceil(USER_DATA_WIDTH/8) | Check_Type & USER_DATA_WIDTH | OC | N | N | N |

| PRUSERCHK | ceil(USER_DATA_WIDTH/8) | Check_Type & USER_DATA_WIDTH | OC | N | N | N |

| PBUSERCHK | ceil(USER_RESP_WIDTH/8) | Check_Type & USER_RESP_WIDTH | OC | N | N | N |

表B-3 展示了接口属性

如果一个条目不是Y,则该接口类型的属性必须为False或未声明

表 B-3 接口属性

| Property | Issue introduced | APB5 | APB4 | APB3 | APB2 |

|---|---|---|---|---|---|

| Check_Type | D | y | — | ||

| USER_REQ_WIDTH | D | y | — | ||

| USER_DATA_WIDTH | D | y | — | ||

| USER_RESP_WIDTH | D | y | — | ||

| Wakeup_Signal | D | y | — |

附录C 版本

本附录描述了本书已发布版本之间的技术变化:

表 C-1 版本A

| 变化 | 位置 |

|---|---|

| 第一次发布 | - |

表 c-2 版本B和版本A的区别

| 变化 | 位置 |

|---|---|

| 增加了信号PREADY | 表 2-13.1 写传输3.3 读传输3.4 ERROR响应第4章 操作状态 |

| 增加了信号PSLVERR | 表 2-13.4 ERROR响应 |

表 C-3 版本C和版本B的区别

| 变化 | 位置 |

|---|---|

| 新增章节列出了在每次修订该文档时所做的更改。 | 附录C 版本 |

| 增加了信号PPROT | 表 2-13.5 保护单元支持 |

| 增加了信号PSTRB | 表 2-13.2 脉冲写 |

表 C-4 版本D和版本C的区别

| 变化 | 位置 |

|---|---|

| 增加了位宽属性 | 2.1 AMBA APB信号 |

| 增加了信号PWAKEUP | 3.7 唤醒信号 |

| 增加了user信号 | 3.8 user信号 |

| 增加了接口校验 | 第5章 奇偶校验接口保护 |

| 规范化术语,使用Completer和Requester | 整个规范 |

| 增加了信号有效性规则 | 附录A 信号有效性 |

| 增加了信号汇总 | 附录B 信号列表 |

表 C-5 版本E和版本D的区别

| 变化 | 位置 |

|---|---|

| 加入了对RME的支持 | 3.6 Realm管理扩展,RME |